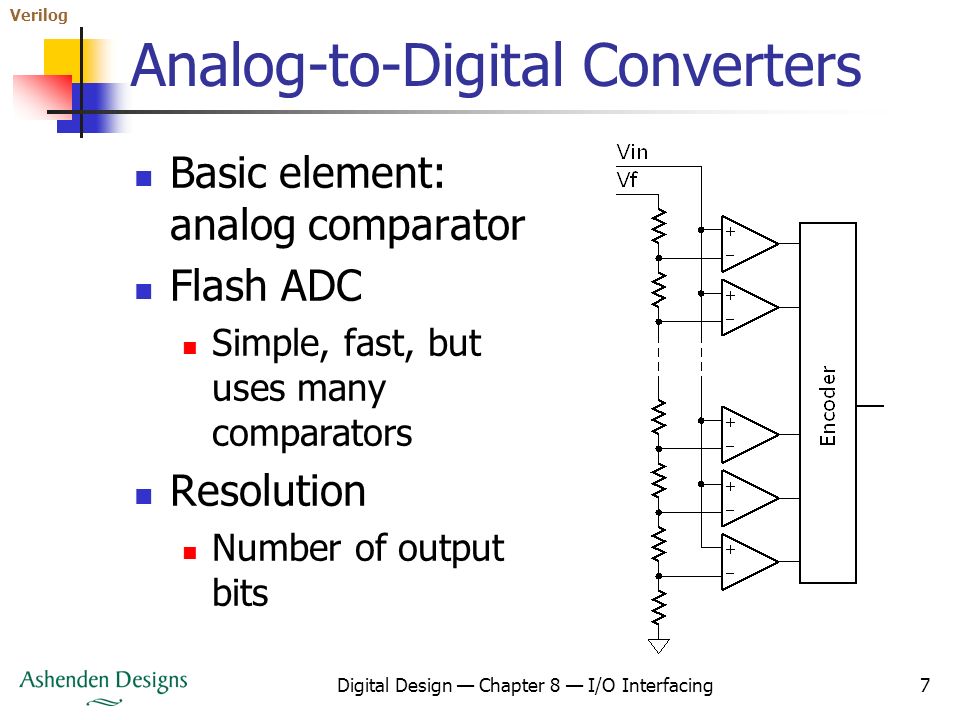

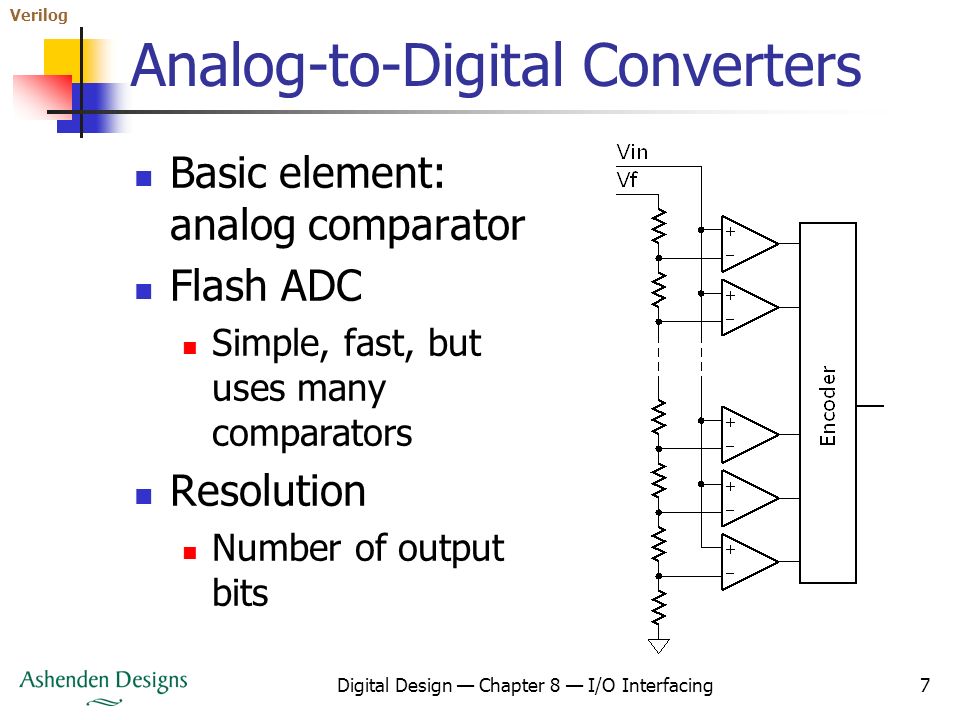

8 Bit Serial To Parallel Converter Verilog Code Average ratng: 4,6/5 7760 reviews

Wrote: > One thing I do not understand is, that dout as std_logic_vector is > displayed as 'uninitialized' every other CLK-cycle - though each > individual bit of the std_logic_vector is showing a well defined logic > value. Mar 15, 2018 - It works for me. That code can no be turned into gates. You must use 'posedge clk' or 'negedge clk'. Also your load is a-synchronous.

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 module piso1 (sout,sin,clk ); output sout; input [ 3: 0 ]sin; input clk; wire [ 3: 0 ]q; inv u1 (p,sl ); and1 u2 (n,sin [ 1 ],p ); and1 u3 (r,sl,q [ 0 ] ); or1 u4 (s,n,r ); and1 u5 (t,sin [ 2 ],p ); and1 u6 (u,sl,q [ 1 ] ); or1 u7 (v,u,t ); and1 u8 (w,sin [ 3 ],p ); and1 u9 (y,sl,q [ 2 ] ); or1 u10 (z,w,y ); dff1 u11 (q [ 0 ],sin [ 0 ],clk ); dff1 u12 (q [ 1 ],s,clk ); dff1 u13 (q [ 2 ],v,clk ); dff1 u14 (q [ 3 ],z,clk ); assign sout = q [ 3 ]; endmodule.

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 module piso1 (sout,sin,clk ); output sout; input [ 3: 0 ]sin; input clk; wire [ 3: 0 ]q; inv u1 (p,sl ); and1 u2 (n,sin [ 1 ],p ); and1 u3 (r,sl,q [ 0 ] ); or1 u4 (s,n,r ); and1 u5 (t,sin [ 2 ],p ); and1 u6 (u,sl,q [ 1 ] ); or1 u7 (v,u,t ); and1 u8 (w,sin [ 3 ],p ); and1 u9 (y,sl,q [ 2 ] ); or1 u10 (z,w,y ); dff1 u11 (q [ 0 ],sin [ 0 ],clk ); dff1 u12 (q [ 1 ],s,clk ); dff1 u13 (q [ 2 ],v,clk ); dff1 u14 (q [ 3 ],z,clk ); assign sout = q [ 3 ]; endmodule.

I want to convert 8 bit serial data into 8 bit parallel data my code is here library IEEE; use IEEE.STD_LOGIC_1164.all; entity PAR2SER is port( din: in STD_LOGIC; clk: in STD_LOGIC; reset: in STD_LOGIC; dout: out STD_LOGIC_VECTOR(7 downto 0) ); end PAR2SER; architecture sipo_behavior_arc of PAR2SER is begin sipo: process (clk,din,reset) is variable s: std_logic_vector(7 downto 0):= '00000000'; begin if (reset='1') then s:= '00000000'; elsif (rising_edge (clk)) then s:= (din & s(7 downto 1)); end if; dout. The waveform looks somewhat strange cause the simulation includes timing: the individual bits of dout switch with some delay with respect to the positive CLK-edge (~6ns. If one takes this delay in consideration and looks at dout only at the 'next' rsising CLK-edge, then dout toggles between xAA and x55 - just as it should when din toggles with every CLK-cycle.

One thing I do not understand is, that dout as std_logic_vector is displayed as 'uninitialized' every other CLK-cycle - though each individual bit of the std_logic_vector is showing a well defined logic value. Besides that the simu just shows, what one should expect from the given description. (By the way: Ser2Par would be a much more appropriate name for this component than Par2Ser). >Instrukciya po montazhu petli blum. but i am not getting correct data.

For me the wavrform looks fine: in the shift register is '01010101' or '10101010' at the rising edge of clk. What could you expect instead? BTW: do a behavioural simulation instead of this post route timing simulation. It makes things much easier and more obvious. > One thing I do not understand is, that dout as std_logic_vector is > displayed as 'uninitialized' every other CLK-cycle - though each > individual bit of the std_logic_vector is showing a well defined logic > value. That looks really kind of strange.